# Allen-Bradley

FLEX I/O 2 Input Incremental Encoder Module (Cat. No. 1794-ID2 Series B)

# User Manual

#### **Important User Information**

Because of the variety of uses for the products described in this publication, those responsible for the application and use of this control equipment must satisfy themselves that all necessary steps have been taken to assure that each application and use meets all performance and safety requirements, including any applicable laws, regulations, codes and standards.

The illustrations, charts, sample programs and layout examples shown in this guide are intended solely for example. Since there are many variables and requirements associated with any particular installation, Allen-Bradley does not assume responsibility or liability (to include intellectual property liability) for actual use based upon the examples shown in this publication.

Allen-Bradley publication SGI–1.1, "Safety Guidelines For The Application, Installation and Maintenance of Solid State Control" (available from your local Allen-Bradley office) describes some important differences between solid-state equipment and electromechanical devices which should be taken into consideration when applying products such as those described in this publication.

Reproduction of the contents of this copyrighted publication, in whole or in part, without written permission of Allen–Bradley Company, Inc. is prohibited.

Throughout this manual we make notes to alert you to possible injury to people or damage to equipment under specific circumstances.

**ATTENTION:** Identifies information about practices or circumstances that can lead to personal injury or death, property damage, or economic loss.

#### Attention helps you:

- identify a hazard

- avoid the hazard

- recognize the consequences

**Important:** Identifies information that is especially important for successful application and understanding of the product.

**Important:** We recommend you frequently backup your application programs on appropriate storage medium to avoid possible data loss.

DeviceNet, DeviceNetManager, and RediSTATION are trademarks of Allen-Bradley Company, Inc. PLC, PLC-2, PLC-3, and PLC-5 are registered trademarks of Allen-Bradley Company, Inc. Windows is a trademark of Microsoft.

Microsoft is a registered trademark of Microsoft

IBM is a registered trademark of International Business Machines, Incorporated.

All other brand and product names are trademarks or registered trademarks of their respective companies.

# **Summary of Changes**

The information contained in this manual pertains to the series B version of the 1794-ID2 frequency input module.

#### **New Information**

This version of this publication contains information on control word 2, for setting the filter function for the counters. This filter information is contained in chapter 1 and identified in chapters 4 and 5.

## **Updated Information**

The vibration specifications for this module have been updated. The specification is as follows:

| Environmental Conditions |                                                                                                                                                                          |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operational Temperat     | ure 0 to 55°C (32 to 131°F) <b>Note:</b> Do not connect maximum input voltage simultaneously to all inputs if the module ambient temperature is expected to exceed 40°C. |

| Storage Temperature      | -40 to 85°C (-40 to 185°F)                                                                                                                                               |

| Relative Humidity        | 5 to 90% noncondensing (operating)                                                                                                                                       |

| •                        | 5 to 80% noncondensing (nonoperating)                                                                                                                                    |

| Shock Operating          | 30g peak acceleration, 11(+1)ms pulse width                                                                                                                              |

| Nonoperating             | 50g peak acceleration, $11(+1)$ ms pulse width                                                                                                                           |

| Vibration                | Tested 50g @ 10-500Hz per IEC 68-2-6                                                                                                                                     |

# **Using This Manual**

#### **Purpose of this Manual**

This manual shows you how to use your FLEX I/O pulse counter module with Allen-Bradley programmable controllers. The manual helps you install, program and troubleshoot your module.

#### **Audience**

You must be able to program and operate an Allen-Bradley programmable controller to make efficient use of your FLEX I/O module. In particular, you must know how to program block transfers.

We assume that you know how to do this in this manual. If you do not, refer to the appropriate programming and operations manual before you attempt to program your modules.

## Vocabulary

In this manual, we refer to:

- the pulse counter module as the "input module"

- the Programmable Controller as the "controller"

### **Manual Organization**

This manual is divided into seven chapters. The following chart lists each chapter with its corresponding title and a brief overview of the topics covered in that chapter.

| Chapter | Title                                                                                      | Contents                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Overview of FLEX I/O and the Pulse Counter Module                                          | Describes FLEX I/O pulse counter modules, features, and how they function                                                          |

| 2       | How to Install Your Pulse Counter<br>Module                                                | How to install and wire the module                                                                                                 |

| 3       | Module Programming                                                                         | Explains block transfer programming, sample programs                                                                               |

| 4       | Writing Configuration to and<br>Reading Status From with a<br>Remote I/O Adapter           | Explains how to configure your modules and read status information from your modules when using a remote I/O adapter               |

| 5       | How Communication Takes Place<br>and I/O Image Table Mapping<br>with the DeviceNet Adapter | Explains how you communicate with your modules, and how the I/O image is mapped when using a DeviceNet adapter                     |

| 6       | Input, Output and Configuration files for Analog Modules using ControlNet                  | Explains how you communicate with your modules, and how the I/O and configuration files are mapped when using a ControlNet adapter |

| 7       | Calibrating Your Pulse Counter Module                                                      | How to calibrate the module.                                                                                                       |

| 8       | Troubleshoot Your Pulse Counter Module                                                     | How to use the indicators to troubleshoot your module.                                                                             |

| Appendix | Title          | Contents                                    |

|----------|----------------|---------------------------------------------|

| Α        | Specifications | Specifications for the pulse counter module |

## **Conventions**

We use these conventions in this manual:

| In this manual, we show:                                                       | Like this: |

|--------------------------------------------------------------------------------|------------|

| that there is more information about a topic in another chapter in this manual |            |

| that there is more information about the topic in another manual               | More       |

## **For Additional Information**

For additional information on FLEX I/O systems and modules, refer to the following documents:

| Ostolon           |         |                                                   | Public                       | Publications   |  |  |

|-------------------|---------|---------------------------------------------------|------------------------------|----------------|--|--|

| Catalog<br>Number | Voltage | Description                                       | Installation<br>Instructions | User<br>Manual |  |  |

| 1794              |         | 1794 FLEX I/O Product Data                        | 1794-2.1                     |                |  |  |

| 1794-ACN          | 24V dc  | ControlNet Adapter                                | 1794-5.8                     |                |  |  |

| 1794-ACNR         | 24V dc  | Redundant Media ControlNet Adapter                | 1794-5.18                    |                |  |  |

| 1794-ACN15        | 24V dc  | ControlNet Adapter                                | 1794-5.47                    |                |  |  |

| 1794-ACNR15       | 24V dc  | Redundant Media ControlNet Adapter                | 1794-5.48                    |                |  |  |

| 1794-ADN          | 24V dc  | DeviceNet Adapter                                 | 1794-5.14                    | 1794-6.5.5     |  |  |

| 1794-ASB/C        | 24V dc  | Remote I/O Adapter                                | 1794-5.50                    | 1794-6.5.9     |  |  |

| 1794-ASB2/B       | 24V dc  | 2-Slot Remote I/O Adapter                         | 1794-5.44                    | 1794-6.5.13    |  |  |

| 1794-APB          | 24V dc  | Profibus Adapter                                  | 1794-5.40                    | 1794-6.5.6     |  |  |

| 1794-IB8          | 24V dc  | 8 Sink Input Module                               | 1794-5.30                    |                |  |  |

| 1794-OB8          | 24V dc  | 8 Source Output Module                            | 1794-5.31                    |                |  |  |

| 1794-IB16         | 24V dc  | 16 Sink Input Module 179                          |                              |                |  |  |

| 1794-OB16         | 24V dc  | 16 Source Output Module                           | 1794-5.3                     |                |  |  |

| 1794-IV16         | 24V dc  | 16 Source Input Module                            | 1794-5.28                    |                |  |  |

| 1794-OV16         | 24V dc  | 16 Sink Output Module                             | 1794-5.29                    |                |  |  |

| 1794-OB8EP        | 24V dc  | lc 8 Electronically Fused Output Module 1794-5.20 |                              |                |  |  |

| 1794-IB8S         | 24V dc  | dc Sensor Input Module 1794-5.                    |                              |                |  |  |

| 1794-IB10XOB6     | 24V dc  | 10 Input/6 Output Module                          | 1794-5.24                    |                |  |  |

| 1794-IE8          | 24V dc  | dc Selectable Analog 8 Input Module 1794-5.6      |                              | 1704 0 5 0     |  |  |

| 1794-OE4          | 24V dc  | Selectable Analog 4 Output Module                 | 1794-5.5                     | 1794-6.5.2     |  |  |

|                   |         | Table continued on next page                      | -                            |                |  |  |

| Ontolon              | Catalon |                                              | Public                       | ations         |

|----------------------|---------|----------------------------------------------|------------------------------|----------------|

| Catalog<br>Number    | Voltage | Description                                  | Installation<br>Instructions | User<br>Manual |

| 1794-IE4XOE2         | 24V dc  | 4 Input/2 Output Analog Module               | 1794-5.15                    | 1794-6.5.2     |

| 1794-OF4             | 24V dc  | 4 Output Isolated Analog Module              | 1794-5.37                    |                |

| 1794-IF4             | 24V dc  | 4 Input Isolated Analog Module               | 1794-5.38                    | 1794-6.5.8     |

| 1794-IF2XOF2         | 24V dc  | 2 Input/2 Output Isolated Analog Module      | 1794-5.39                    |                |

| 1794-IR8             | 24V dc  | 8 RTD Input Analog Module                    | 1794-5.22                    | 1794-6.5.4     |

| 1794-IT8             | 24V dc  | 8 Thermocouple Input Module                  | 1794-5.21                    | 1794-6.5.7     |

| 1794-IRT8            | 24V dc  | 8 Thermocouple/RTD Input Module              | 1794-5.50                    | 1794-6.5.12    |

| 1794-IJ2             | 24V dc  | 2 Frequency Input Module                     | 1794-5.49                    | 1794-6.5.11    |

| 1794-IA8             | 120V ac | 8 Input Module                               | 1794-5.9                     |                |

| 1794-OA8             | 120V ac | Output Module                                | 1794-5.10                    |                |

| 1794-TB2<br>1794-TB3 |         | 2-wire Terminal Base<br>3-wire Terminal Base | 1794-5.2                     |                |

| 1794-TBN             |         | Terminal Base Unit                           | 1794-5.16                    |                |

| 1794-TBNF            | 1       | Fused Terminal Base Unit                     | 1794-5.17                    |                |

| 1794-TB3T            |         | Temperature Terminal Base Unit               | 1794-5.41                    |                |

| 1794-TB3S            | 1       | Spring Clamp Terminal Base Unit              | 1794-5.42                    |                |

| 1794-TB3TS           | 1       | Spring Clamp Temperature Base Unit           | 1794-5.43                    |                |

| 1794-TB3G            | 1       | Terminal Base Unit                           | 1794-5.51                    |                |

| 1794-TB3GS           |         | Spring Clamp Terminal Base Unit              | 1794-5.59                    |                |

| 1794-CE1, -CE3       |         | Extender Cables                              | 1794-5.12                    |                |

| 1794-NM1             |         | Mounting Kit 1794-2.13                       |                              |                |

| 1794-PS1             | 24V dc  | Power Supply                                 | 1794-5.35                    |                |

# **Summary**

This preface gave you information on how to use this manual efficiently. The next chapter introduces you to the frequency module.

| Overview of the incremental | Chapter 1                                                         |      |

|-----------------------------|-------------------------------------------------------------------|------|

| Encoder Module              | What This Chapter Contains                                        | 1-1  |

|                             | How You Use the Incremental Encoder Module                        | 1-1  |

|                             | What the Incremental Encoder Module Does                          | 1-2  |

|                             | Typical Applications                                              | 1-3  |

|                             | Input Capabilities                                                | 1-3  |

|                             | How the Incremental Encoder Operates                              | 1-4  |

|                             | Variables                                                         | 1-4  |

|                             | Start Counting                                                    | 1-4  |

|                             | Selecting the incremental encoder and up/down counting            | 1-4  |

|                             | Up/Down Counting Controlled by B Input                            | 1-5  |

|                             | Up/Down Counting using Pulses at Inputs A and B                   | 1-5  |

|                             | Count Pulses from Incremental Encoders                            | 1-6  |

|                             | Preset Function                                                   | 1-7  |

|                             |                                                                   | 1-7  |

|                             | Gate Function                                                     | 1-7  |

|                             | Store Function                                                    | 1-8  |

|                             | Limitation Function                                               | 1-8  |

|                             | Chapter Summary                                                   | 1-9  |

| How to Install Your         | Chapter 2                                                         |      |

| Incremental Encoder Module  | What This Chapter Contains                                        | 2-1  |

|                             | Before You Install Your Input Module                              | 2-1  |

|                             | European Union Directive Compliance                               | 2-1  |

|                             | EMC Directive                                                     | 2-1  |

|                             | Low Voltage Directive                                             | 2-2  |

|                             | Power Requirements                                                | 2-2  |

|                             | Wiring the Terminal Base Units (1794-TB3G shown)                  | 2-3  |

|                             | Installing the Module                                             | 2-4  |

|                             | Mounting the Terminal Base Unit on a DIN Rail                     | 2-4  |

|                             | Panel/Wall Mounting                                               | 2-6  |

|                             | Mounting the Incremental Encoder Module on the Terminal Base Unit | 2-7  |

|                             | Connecting Wiring for Your incremental encoder Module             | 2-9  |

|                             | Wiring to a 1794-TBN or -TBNF Terminal Base Unit                  | 2-11 |

|                             | Wiring connections for the 1794–ID2 incremental encoder Module    | 2-12 |

|                             | Example of Pulse Transmitter Wiring                               | 2-13 |

|                             | Example of Incremental Encoder Wiring                             | 2-13 |

|                             | Module Indicators                                                 | 2-14 |

|                             | Chapter Summary                                                   | 2-14 |

| Programming Your             | Chapter 3                                                                          |            |

|------------------------------|------------------------------------------------------------------------------------|------------|

| Incremental Encoder Module   | What This Chapter Contains                                                         | 3-1<br>3-1 |

|                              | PLC-2 Family Processor                                                             | 3-2        |

|                              | PLC-5 Family Processor                                                             | 3-2        |

|                              | SLC-5 Programming                                                                  | 3–3<br>3–8 |

| Writing Configuration to and | Chapter 4                                                                          |            |

| Reading Status from Your     | What This Chapter Contains                                                         | 4–1        |

| Module with a Remote I/O     | Configuring Your Incremental Encoder Module                                        | 4–1        |

| Adapter                      | Reading Data From Your Module                                                      | 4-2        |

|                              | Mapping Data for the Module                                                        | 4-2        |

|                              | Incremental Encoder Module (1794-ID2) Image Table Mapping                          | 4-2        |

|                              | Block Transfer Read Word Assignments for the Incremental Enco                      |            |

|                              | Module (1794-ID2)                                                                  | 4–3        |

|                              | Bit/Word Definitions for Block Transfer Read Words for the                         |            |

|                              | Incremental Encoder Module                                                         | 4-3        |

|                              | Block Transfer Write Word Assignments for the Incremental Enco                     |            |

|                              | Module                                                                             | 4–5        |

|                              | Bit/Word Definitions for the Block Transfer Write Words for the                    |            |

|                              | Incremental Encoder Module                                                         | 4-5        |

|                              | Chapter Summary                                                                    | 4–7        |

| How Communication Takes      | Chapter 5                                                                          |            |

| Place and I/O Image Table    | What This Chapter Contains                                                         | 5–1        |

| Mapping with the DeviceNet   | About DeviceNetManager Software                                                    | 5–1        |

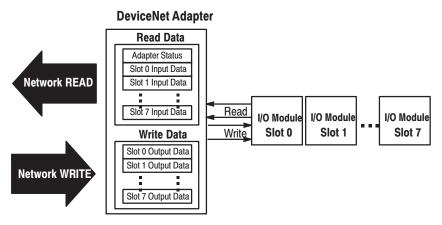

| Adapter                      | Polled I/O Structure                                                               | 5–1        |

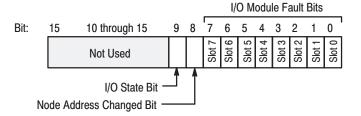

|                              | Adapter Input Status Word                                                          | 5-2        |

|                              | System Throughput                                                                  | 5–3        |

|                              | Mapping Data into the Image Table                                                  | 5–3        |

|                              | Incremental Encoder Module (1794-ID2) Image Table Mapping                          | 5–3        |

|                              | Block Transfer Read Word Assignments for the Incremental Enco<br>Module (1794-ID2) | der<br>5-4 |

|                              | Block Transfer Write Word Assignments for the Incremental Enco                     | der<br>5-4 |

|                              | Bit/Word Definitions for the incremental encoder Module                            |            |

|                              | (1794–ID2)                                                                         | 5–5        |

|                              | Defaults                                                                           | 5-8        |

| Input, Output and            | Chapter 6                                                                                                            |     |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|--|--|

| Configuration Files for      | Chapter Objectives                                                                                                   |     |  |  |

| Analog Modules when used     | About the ControlNet Adapter                                                                                         | 6–1 |  |  |

| with ControlNet              | Scheduled Data-Transfer                                                                                              | 6-2 |  |  |

|                              | Unscheduled Data-Transfer                                                                                            | 6-2 |  |  |

|                              | Module I/O Mapping                                                                                                   | 6-2 |  |  |

|                              | I/O Structure                                                                                                        | 6-3 |  |  |

|                              | Adapter Input Status Word                                                                                            | 6-3 |  |  |

|                              | Safe State Data                                                                                                      | 6-4 |  |  |

|                              | Device Actions                                                                                                       | 6-4 |  |  |

|                              | Communication Fault Behavior                                                                                         | 6-5 |  |  |

|                              | Idle State Behavior                                                                                                  | 6-5 |  |  |

|                              | Input Data Behavior upon Module Removal                                                                              | 6-5 |  |  |

|                              | Incremental Encoder Module (1794-ID2) Image Table Mapping Bit/Word Definitions for Block Transfer Read Words for the |     |  |  |

|                              | Pulse Counter Module                                                                                                 | 6-6 |  |  |

| Calibrating Your Incremental | Chapter 7                                                                                                            |     |  |  |

| Encoder Module               | Chapter Objective                                                                                                    | 7–1 |  |  |

|                              | Calibrating Your Module                                                                                              | 7–1 |  |  |

|                              | Calibration Method 1                                                                                                 | 7-2 |  |  |

|                              | Calibration Method 2                                                                                                 | 7–3 |  |  |

| Troubleshoot the             | Chapter 8                                                                                                            |     |  |  |

| Incremental Encoder Module   | What This Chapter Contains                                                                                           | 8–1 |  |  |

|                              | Status Indicators                                                                                                    | 8–1 |  |  |

|                              | What's Next                                                                                                          | 8-2 |  |  |

| Specifications               | Appendix A                                                                                                           |     |  |  |

| -                            | Specifications                                                                                                       | A-1 |  |  |

# **Overview of the Incremental Encoder Module**

# What This Chapter Contains

Read this chapter to familiarize yourself with the 1794–ID2 module.

| For information on                         | See page |

|--------------------------------------------|----------|

| How You Use the incremental encoder Module | 1–1      |

| What the incremental encoder Module Does   | 1-2      |

| Input Capabilities                         | 1-3      |

| How the incremental encoder Operates       | 1-4      |

# How You Use the incremental encoder Module

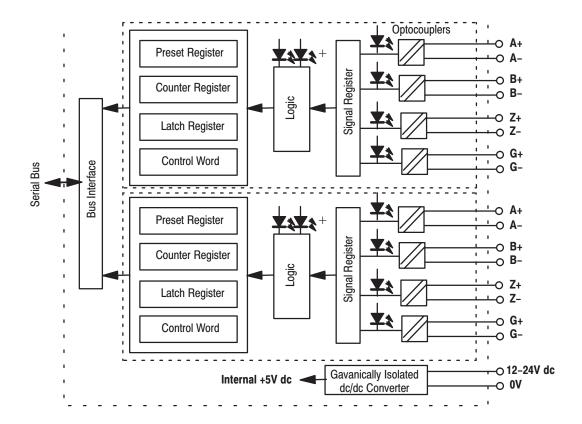

The 1794–ID2 module is an intelligent I/O module designed to perform high speed pulse counting. The module provides:

• 2 pulse transmitter interfaces, each with 4 optocoupled inputs Each input has + and – inputs for connection to transmitters with complementary and noncomplementary signals.

The pulse inputs can accept frequencies up to 100KHz. The module accepts and returns binary data.

The module's primary use is accurate, high-speed counting of pulse from pulse transmitters or incremental encoders with 1 or 2 pulse trains. This includes quantity counting, positioning and speed calculations.

The module has 2 up/down counters, each individually programmable. The number of edges to be counted can be multiplied by 1, 2 or 4 (x1, x2, x4). Pulse transmitters can be complementary or noncomplementary.

#### What the Incremental Encoder Module Does

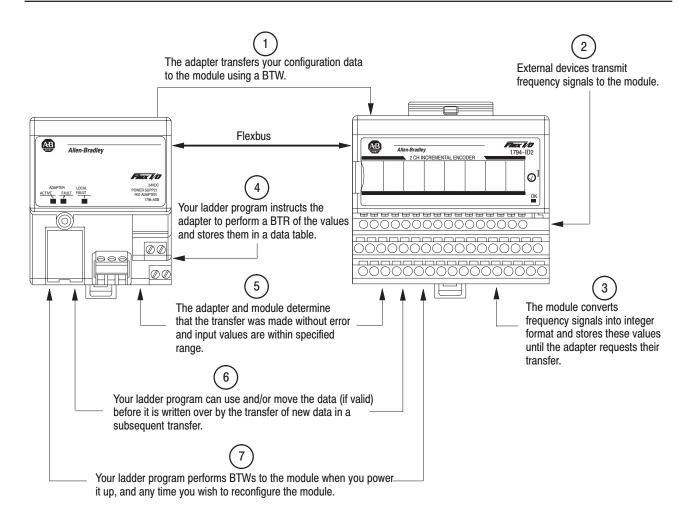

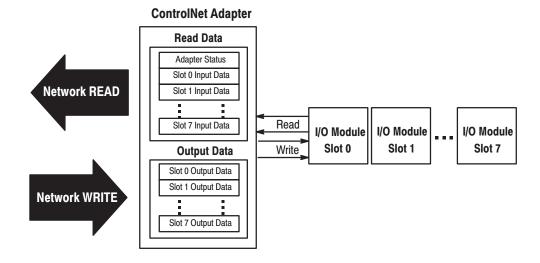

The incremental encoder module performs high-speed scaling calculation operations for various industrial applications. The module interfaces with a FLEX family adapter which then communicates with a programmable controller processor that has block-transfer capability and external I/O devices.

The adapter/power supply transfers data to the module (block transfer write) and from the module (block transfer read) using BTW and BTR instructions in your ladder diagram program. These instructions let the adapter read input values and status from the module, and let you write output values and configure the module's mode of operation. The following illustration describes the communication process.

### **Typical Applications**

You can use the 1794–ID2 module in the power management, automotive, food and beverage, and oil and gas industries for various flow and/or turbine metering applications. Some sample applications include:

- turbine shaft speed monitoring

- automotive paint booths

- brewery flow monitoring

- petrochemical flow and custody transfer

## **Input Capabilities**

The incremental encoder module has 2 identical input channels. Each of the input channels may accept these input signals:

- A+ and A-

- B+ and B-

- Z+ and Z-

- G+ and G-

The pulse inputs can accept frequencies up to 100KHz. The module accepts and returns binary data.

# How the incremental encoder Operates

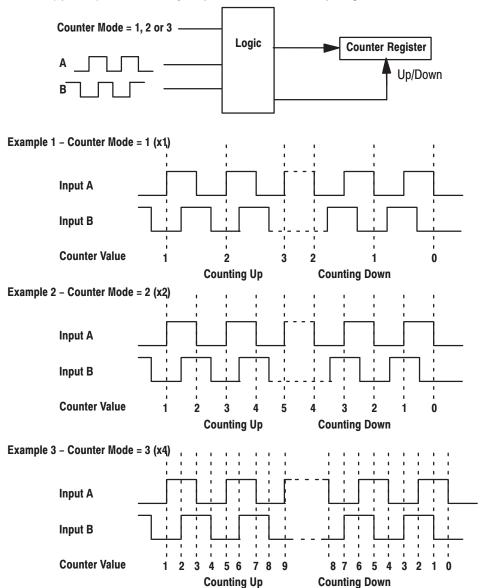

The counter module handles up/down counting and detection of selectable number of edges (X1, X2, X4) for incremental encoders with 2 pulse trains, nominal  $90^{\rm o}$  out of phase. The minimum stable input condition is  $2\mu s$ . The following paragraphs detail operation of the incremental encoder module.

Each of the 2 counters has a 16-bit counter register, a preset register and a latch register.

#### **Variables**

Communication between the counter module and the control system uses variables accessible in the control system program. These variables include:

- a counter register (Counter)

- a preset register (*PresetValue*)

- a latch register (*LatchValue*).

Signal registers and control words are used to set parameters for the counter configuration. The control word sent to the incremental encoder module can be read back to the control system, allowing verification that one I/O scan been performed since the cycle has been initiated.

#### **Start Counting**

The control bit CounterEnable enables counting. It must be set to 1 to enable counting and all other functions.

#### Selecting the incremental encoder and up/down counting

Depending on the incremental encoder, the module can be set in different counter modes. The parameter is set using a 3 digit code in write word 1 or 2 (depending on the channel) control word.

| Mod | Mode Selection |    |    |                                                                                                  |  |  |  |

|-----|----------------|----|----|--------------------------------------------------------------------------------------------------|--|--|--|

| Bit | 02             | 01 | 00 | Mode Selection bits                                                                              |  |  |  |

|     | 0              | 0  | 0  | Counting on positive (rising) edge of input signal A. (Up/dwn counting determined by B.)         |  |  |  |

|     | 0              | 0  | 1  | Quadrature encoder X1                                                                            |  |  |  |

|     | 0              | 1  | 0  | Quadrature encoder X2                                                                            |  |  |  |

|     | 0              | 1  | 1  | Quadrature encoder X4                                                                            |  |  |  |

|     | 1              | 0  | 0  | Counting up on the positive edge of input signal A, and down on positive edge of input signal B. |  |  |  |

|     | 1              | 0  | 1  | No count function.                                                                               |  |  |  |

|     | 1              | 1  | 0  | No count function.                                                                               |  |  |  |

|     | 1              | 1  | 1  | No count function.                                                                               |  |  |  |

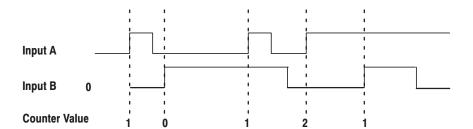

#### **Up/Down Counting Controlled by B Input**

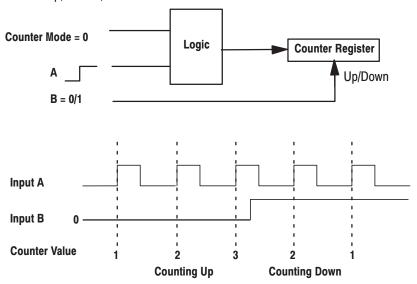

#### **Pulse Counting (Mode 000)**

#### Up/Down counting controlled by input B

The positive edge of the pulses are counted at input A. If input B=0, the counter counts up; if B=1, the counter counts down.

#### Up/Down Counting using Pulses at Inputs A and B

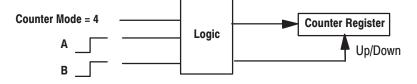

#### **Pulse Counting Mode (100)**

Up/Down Counting using pulses at the inputs of A and B

The counter counts up on the positive edge of the pulses at input A, and counts down on the positive edge of input B.

#### **Count Pulses from Incremental Encoders**

#### Pulse Counting Mode (001, 010. 011) Up/Down Counting using pulses at the inputs of A and B

If countermode = 1, 2 or 3, then 1, 2 or 4 edges of the pulse train will be counted. The count direction (up/down) is determined by the phase difference of the input signals A and B.

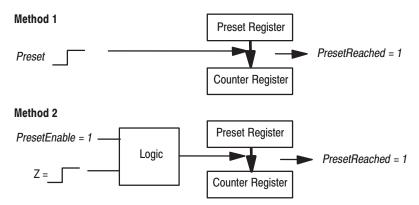

#### **Preset Function**

Use the preset function to copy a value from the preset register to the counter register.

The flag PresetReached is set when the counter register and the preset register are equal (if the counter preset is reached, or if the counter has been loaded with the preset value). This flag is reset on a positive edge of PresetReset after the operation and can only be set after at least one additional counting pulse.

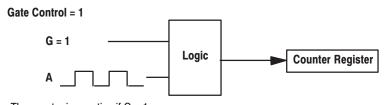

#### **Gate Function**

Use the gate function to determine when counting starts and stops. You can use this function to measure distance.

The parameter GateControl determines the gate function. The gate signal is connected to input G. It is a 2-bit binary code in write word 1 or 2, bits 09 and 10

| Word<br>1 or 2 |               | Gate Control Function |    |    |                                                                                                           |

|----------------|---------------|-----------------------|----|----|-----------------------------------------------------------------------------------------------------------|

|                | Bits<br>09-10 | Binary                | 10 | 09 | Gate Control bits                                                                                         |

|                |               | 0                     | 0  | 0  | No gate function on input G (Count is independent)                                                        |

|                |               | 1                     | 0  | 1  | Counting only if G = 1 (active)                                                                           |

|                |               | 2                     | 1  | 0  | Counting only if G = 0 (inactive)                                                                         |

|                |               | 3                     | 1  | 1  | Calibration if G = 1 and all other conditions are fulfilled (refer to Calibrating the Module, chapter ?). |

#### **Example**

The counter is counting if G=1.

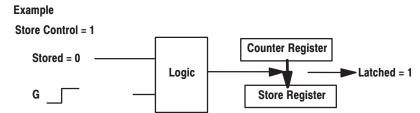

#### **Store Function**

Use the store function to copy the value in the counter register (*Counter*) to the latch register (*StoreValue*).

The StoreControl parameter determines the store function. Execution occurs on either the positive or negative edge of input signals G and Z respectively (see table). The parameter is a 2–bit binary code in write word 1 (bits 11 and 12)

| Word<br>1 or 2 | Bits<br>11-12 | Binary | 12 | 11 | Store Control bits                                                                        |  |

|----------------|---------------|--------|----|----|-------------------------------------------------------------------------------------------|--|

|                |               | 0      | 0  | 0  | Save the counter value on the positive edge of Z (if Stored X = 0)                        |  |

|                |               | 1      | 0  | 1  | Save the counter value on the positive edge of G (if Stored X = 0)                        |  |

|                |               | 2      | 1  | 0  | Save the counter value on the negative edge of G (if Stored X = 0)                        |  |

|                |               | 3      | 1  | 1  | Save the counter value on both the positive edge and negative edge of G (if Stored X = 0) |  |

The parameter *Stored* must be reset (0). Stored is set (1) when the operation is completed. Reset after the operation with *StoreReset*.

The counter value is copied to the store register on the positive edge of input signal G.

#### **Limitation Function**

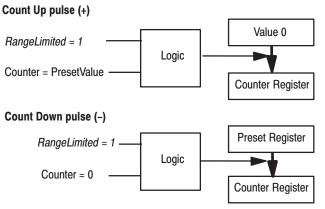

If the control bit RangeLimited = 1, the counter counts up to the preset value and restarts at 0. Counting down, the counter reaches the preset value on the next pulse if the current counter value = 0.

RangeLimited = 0 corresponds to RangeLimited = 1 if the preset value = FFFF in hex = 65535 in decimal.

The flag *PresetReached* is set when the counter is equal to the preset value. Use *PresetReset* to reset the flag.

**Note:** If the preset register value = 0, the counter retains the value 0.

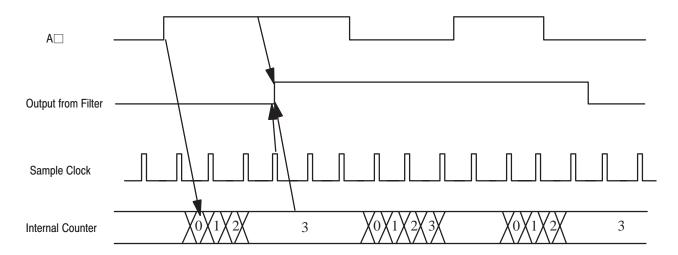

#### **Filter Function**

The filter function is only valid during mode 000 (pulse counting). You enable the filter function by setting bits in Control word 2. Each counter can be individually filtered by enabling its associated filter control bit. However the filter is common to both counters.

When a counter is in mode 000 and its filter is enabled, signal A is internally sampled at a rate 8 times higher than the filter constant. A change of state in A has to be valid during 4 samples before it reaches the counter.

# **Chapter Summary**

In this chapter, you learned about the incremental encoder module, block transfer communication, and details of how the module functions. Now you can install the module.

## How to Install Your Incremental Encoder Module

# What This Chapter Contains

In this chapter, we tell you about:

| For information on             | See page |

|--------------------------------|----------|

| Before You Install Your Module | 2–1      |

| European Union Directives      | 2-1      |

| Power Requirements             | 2-2      |

| Installing the Module          | 2-4      |

| on a DIN rail                  | 2-4      |

| on a wall/panel                | 2-6      |

| on the terminal base           | 2-7      |

| Connecting Wiring              | 2-9      |

| Module Indicators              | 2–14     |

# Before You Install Your Input Module

Before installing your incremental encoder module in the FLEX I/O system:

| You need to:                                                         | As described under:             |

|----------------------------------------------------------------------|---------------------------------|

| Calculate the power requirements of all modules in each FLEX system. | Power Requirements, page 2-2    |

| Position the keyswitch on the terminal base                          | Installing the Module, page 2-4 |

**ATTENTION:** The incremental encoder module does not receive power from the backplane. +24V dc power must be applied to your module before installation. If power is not applied, the module position will appear to the adapter as an empty slot in your chassis.

# **European Union Directive Compliance**

If this product has the CE mark it is approved for installation within the European Union and EEA regions. It has been designed and tested to meet the following directives.

#### **EMC Directive**

This product is tested to meet Council Directive 89/336/EEC Electromagnetic Compatibility (EMC) and the following standards, in whole or in part, documented in a technical construction file:

- EN 50081-2EMC Generic Emission Standard, Part 2 Industrial Environment

- EN 50082-2EMC Generic Immunity Standard, Part 2 Industrial Environment

This product is intended for use in an industrial environment.

#### **Low Voltage Directive**

This product is tested to meet Council Directive 73/23/EEC Low Voltage, by applying the safety requirements of EN 61131–2 Programmable Controllers, Part 2 – Equipment Requirements and Tests.

For specific information required by EN 61131-2, see the appropriate sections in this publication, as well as Allen-Bradley publication 1770-4.1, Industrial Automation Wiring and Grounding Guidelines.

Open style devices must be provided with environmental and safety protection by proper mounting in enclosures designed for specific application conditions. See NEMA Standards publication 250 and IEC publication 529, as applicable, for explanations of the degrees of protection provided by different types of enclosure.

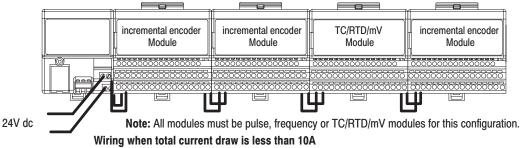

### **Power Requirements**

The wiring of the terminal base unit is determined by the current draw through the terminal base. Make certain that the current draw does not exceed 10A.

**ATTENTION:** Total current draw through the terminal base unit is limited to 10A. Separate power connections may be necessary.

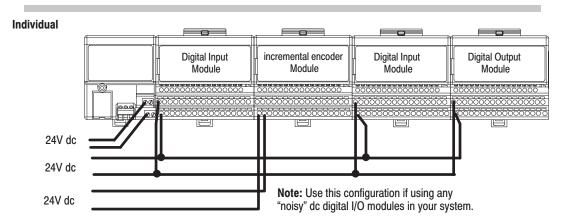

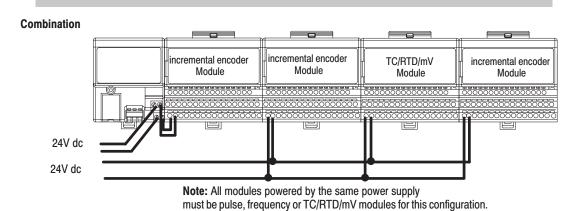

Methods of wiring the terminal base units are shown in the illustration below.

#### Wiring the Terminal Base Units (1794-TB3G shown)

**ATTENTION:** Do not daisy chain power or ground from the terminal base unit to any ac or dc digital module terminal base unit.

#### **Daisy-chaining**

incremental encoder Module wiring separate from digital wiring.

#### Wiring when total current draw is greater than 10A

Total current draw through any base unit must not be greater than 10A

#### **Installing the Module**

Installation of the incremental encoder module consists of:

- mounting the terminal base unit

- installing the module into the terminal base unit

- installing the connecting wiring to the terminal base unit

If you are installing your module into a terminal base unit that is already installed, proceed to "Mounting the incremental encoder Module on the Terminal Base" on page 2–7.

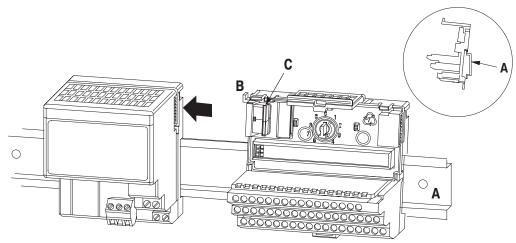

#### Mounting the Terminal Base Unit on a DIN Rail

**ATTENTION:** Do not remove or replace a terminal base unit when power is applied. Interruption of the flexbus can result in unintended operation or machine motion.

- 1. Remove the cover plug (if used) in the male connector of the unit to which you are connecting this terminal base unit.

- **2.** Check to make sure that the 16 pins in the male connector on the adjacent device are straight and in line so that the mating female connector on this terminal base unit will mate correctly.

- **3.** Position the terminal base on the 35 x 7.5mm DIN rail **A** (A-B pt. no. 199-DR1; 46277-3). Proceed as follows:

Position terminal base at a slight angle and hooked over the top of the DIN rail.

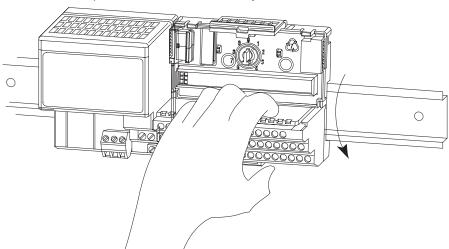

**4.** Make certain that the female flexbus connector **C** is **fully retracted** into the base unit.

Slide the terminal base unit over tight against the adapter. Make sure the hook on the terminal base slides under the edge of the adapter and the flexbus connector is fully retracted.

Press down on the terminal base unit to lock the terminal base on the DIN rail. If the terminal base does not lock into place, use a screwdriver or similar device to open the locking tab, press down on the terminal base until flush with the DIN rail and release the locking tab to lock the base in place.

30077-M

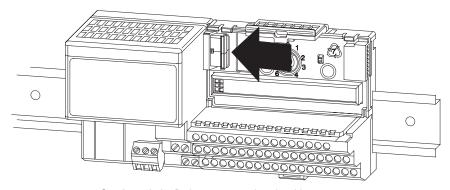

**Gently** push the flexbus connector into the side of the adapter to complete the backplane connection.

**5.** Repeat the above steps to install the next terminal base.

#### **Panel/Wall Mounting**

Installation on a wall or panel consists of:

- laying out the drilling points on the wall or panel

- drilling the pilot holes for the mounting screws

- mounting the adapter mounting plate

- installing the terminal base units and securing them to the wall or panel

If you are installing your module into a terminal base unit that is already installed, proceed to "Mounting the incremental encoder Module on the Terminal Base" on page 2–7.

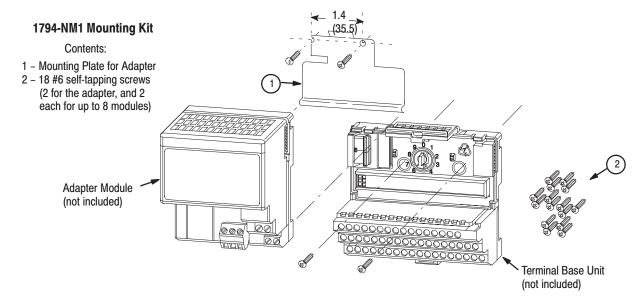

Use the mounting kit Cat. No. 1794-NM1 for panel/wall mounting.

To install the mounting plate on a wall or panel:

**1.** Lay out the required points on the wall/panel as shown in the drilling dimension drawing.

#

#### Drilling Dimensions for Panel/Wall Mounting of FLEX I/O

- **2.** Drill the necessary holes for the #6 self-tapping mounting screws.

- **3.** Mount the mounting plate (1) for the adapter module using two #6 self-tapping screws (18 included for mounting up to 8 modules and the adapter).

Important:

Make certain that the mounting plate is properly grounded to the panel. Refer to "Industrial Automation Wiring and Grounding Guidelines," publication 1770-4.1.

- **4.** Hold the adapter (2) at a slight angle and engage the top of the mounting plate in the indention on the rear of the adapter module.

- **5.** Press the adapter down flush with the panel until the locking lever locks.

- **6.** Position the terminal base unit up against the adapter and push the female bus connector into the adapter.

- 7. Secure to the wall with two #6 self-tapping screws.

- **8.** Repeat for each remaining terminal base unit.

**Note:** The adapter is capable of addressing eight modules. Do not exceed a maximum of eight terminal base units in your system.

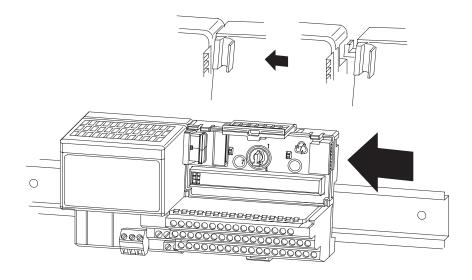

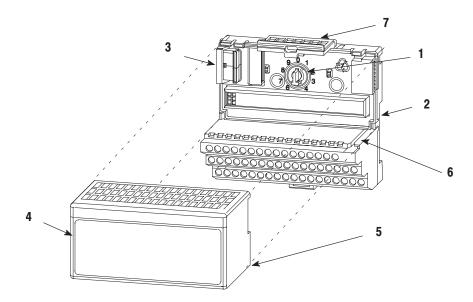

# Mounting the Incremental Encoder Module on the Terminal Base Unit

The incremental encoder module mounts on a 1794-TB3, TB3S, -TBN or -TBNF terminal base unit.

1. Rotate the keyswitch (1) on the terminal base unit (2) clockwise to position 1 as required for the incremental encoder module.

- 2. Make certain the flexbus connector (3) is pushed all the way to the left to connect with the neighboring terminal base/adapter. You cannot install the module unless the connector is fully extended.

- **3.** Make sure that the pins on the bottom of the module are straight so they will align properly with the connector in the terminal base unit.

**ATTENTION:** Remove field-side power before removing or inserting the module. This module is designed so **you can remove and insert it under backplane power.** When you remove or insert a module with field-side power applied, an electrical arc may occur. An electrical arc can cause personal injury or property damage by:

- sending an erroneous signal to your system's field devices causing unintended machine motion

- causing an explosion in a hazardous environment Repeated electrical arcing causes excessive wear to contacts on both the module and its mating connector. Worn contacts may create electrical resistance.

- **4.** Position the module (4) with its alignment bar (5) aligned with the groove (6) on the terminal base.

- **5.** Press firmly and evenly to seat the module in the terminal base unit. The module is seated when the latching mechanism (7) is locked into the module.

- **6.** Repeat the above steps to install the next module in its terminal base unit.

#### **Connecting Wiring for** Your incremental encoder Module

Wiring to the module is made through the terminal base unit on which the module mounts.

Compatible terminal base units are:

| Module   | 1794-TB3 | 1794-TB3S | 1794-TBN | 1794-TBNF |

|----------|----------|-----------|----------|-----------|

| 1794-ID2 | Yes      | Yes       | Yes      | Yes       |

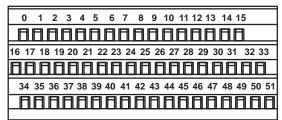

1794-TB3

| 1794-TB3S                                                                                |  |  |

|------------------------------------------------------------------------------------------|--|--|

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 |  |  |

Label placed at top of wiring area. A A A A A A A A A A A A A A A A A A A

34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51

34 and 50 = 24V dc 35 and 51 = common

16 and 33 = chassis ground 40 thru 45 = chassis ground 34 and 50 = 24V dc35 and 51 = common

16 and 33 = chassis ground 40 thru 45 = chassis ground

#### Connecting Wiring using a 1794-TB3 and -TB3S Terminal Base Units

1. Connect individual input wiring (A+, A-, B+, B-, Z+, Z-, G+, G-) to numbered terminals on the **0-15** row (A) as indicated in the table below.

**ATTENTION:** Do not connect maximum input voltage simultaneously to all inputs if the module ambient temperature is expected to exceed 40°C.

**ATTENTION:** If the module ambient temperature is expected to continuously exceed 40°C, you must limit the input voltage using an external resistor on each input. A  $1K\Omega$  resistor effectively limits a 24V sensor signal to about 15V at the input. Do not limit the input to less than 6V.

**2.** Connect the associated input common (3-wire devices only) to the corresponding terminal on the 16-33 row (**B**) for each input as indicated in the table below. (Commons are internally connected together.)

- **3.** Terminate shields to terminals 16 or 33 on row **B**, or 40 through 45 on row **C**.

- **4.** Connect +24V dc to terminal 34 on the **34-51** row (**C**).

- 5. Connect dc return to terminal 16 on the 16–33 row (B).

**ATTENTION:** To reduce susceptibility to noise, power frequency modules and digital modules from separate power supplies. Do not exceed a length of 33 ft (10m) for dc power cabling.

- **6.** If continuing power to the next terminal base unit, connect a jumper from terminal 51 (+24V dc) on this base unit to terminal 34 on the next base unit.

- 7. If continuing common to the next terminal base unit, connect a jumper from terminal 33 (common) on this base unit to terminal 16 on the next base unit.

**ATTENTION:** Do not daisy chain power or ground from this terminal base unit to any ac or dc digital module terminal base unit.

**ATTENTION:** This module does not receive power from the backplane. +24V dc power must be applied to your module before operation. If power is not applied, the module position will appear to the adapter as an empty slot in your chassis. If the adapter does not recognize your module after installation is completed, cycle power to the adapter.

#### Wiring to a 1794-TBN or -TBNF Terminal Base Unit

1. Connect individual input wiring (A+, A-, B+, B-, Z+, Z-, G+, G-) to the even numbered terminals on row (B) as indicated in the table below.

**ATTENTION:** Do not connect maximum input voltage simultaneously to all inputs if the module ambient temperature is expected to exceed 40°C.

**ATTENTION:** If the module ambient temperature is expected to continuously exceed 40°C, you must limit the input voltage using an external resistor on each input. A  $1K\Omega$  resistor effectively limits a 24V sensor signal to about 15V at the input. Do not limit the input to less than 6V.

- 2. Connect the associated input common to the corresponding odd numbered terminal on row (C) for each input as indicated in the table below.

- **3.** Connect 24V dc to terminal 34 on row (C).

- **4.** Connect 24V dc common to terminal 16 on row (**B**).

- **5.** If continuing power to the next terminal base unit, connect a jumper from terminal 51 (24V dc) on this base unit to terminal 34 on the next base unit.

- **6.** If continuing common to the next terminal base unit, connect a jumper from terminal 33 (24V dc common) on this base unit to terminal 16 on the next base unit.

Wiring connections for the 1794-ID2 incremental encoder Module

|                               |                                                                      | ninal Base Unit<br>94–TB3, –TB3S | Terminal Base Units<br>1794–TBN, –TBNF <sup>1</sup> |        |       |

|-------------------------------|----------------------------------------------------------------------|----------------------------------|-----------------------------------------------------|--------|-------|

|                               | Signal                                                               | 0V dc                            | 12/24V dc                                           | Signal | Input |

| incremental encoder Channel 0 |                                                                      |                                  |                                                     |        |       |

| A+                            | 0                                                                    | 17                               | 35                                                  | 0      |       |

| A-                            | 1                                                                    | 18                               | 36                                                  | 1      |       |

| B+                            | 2                                                                    | 19                               | 37                                                  | 2      |       |

| В-                            | 3                                                                    | 20                               | 38                                                  | 3      |       |

| Z+                            | 4                                                                    | 21                               | 39                                                  | 4      |       |

| Z-                            | 5                                                                    | 22                               | 40                                                  | 5      |       |

| G+                            | 6                                                                    | 23                               | 41                                                  | 6      |       |

| G-                            | 7                                                                    | 24                               | 42                                                  | 7      |       |

|                               | inc                                                                  | remental enco                    | der Channel 1                                       |        |       |

| A+                            | 8                                                                    | 25                               | 43                                                  | 8      |       |

| A-                            | 9                                                                    | 26                               | 44                                                  | 9      |       |

| B+                            | 10                                                                   | 27                               | 45                                                  | 10     |       |

| B-                            | 11                                                                   | 28                               | 46                                                  | 11     |       |

| Z+                            | 12                                                                   | 29                               | 47                                                  | 12     |       |

| Z-                            | 13                                                                   | 30                               | 48                                                  | 13     |       |

| G+                            | 14                                                                   | 31                               | 49                                                  | 14     |       |

| G-                            | 15                                                                   | 32                               | 50                                                  | 15     |       |

| 0V dc                         | Terminals 16 and 33 (1794–TB2) Terminals 16 and 33 (1794-TB3, -TB3S) |                                  |                                                     |        |       |

| 12/24V dc                     | Terminals 34 thru 51 (1794–TB3, –3S)  Terminals 34 and 51            |                                  |                                                     |        |       |

<sup>1</sup> Auxiliary terminal blocks are required when using these terminal base units.

**ATTENTION:** Total current draw through the terminal base unit is limited to 10A. Separate power connections to the terminal base unit may be necessary.

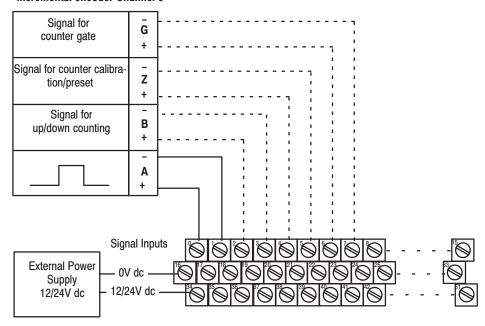

#### **Example of Pulse Transmitter Wiring**

#### incremental encoder Channel 0

Example of pulse transmitter with 1 pulse train. For connection of channel 1, refer to wiring table.

Note: Dotted lines indicate signals not always used.

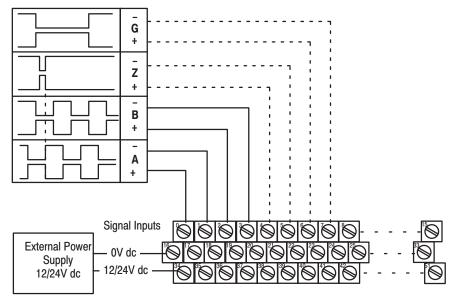

#### **Example of Incremental Encoder Wiring**

#### incremental encoder Channel 0

Example of incremental encoder with 2 pulse trains, with or without reference, and/or gate function. For connection of channel 1, refer to wiring table.

Note: Dotted lines indicate signals not always used.

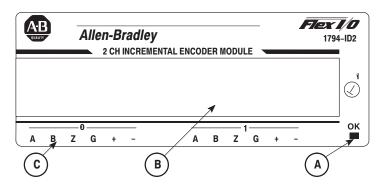

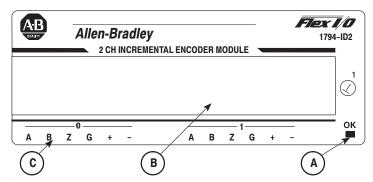

#### **Module Indicators**

The incremental encoder module has one status indicator (PWR) that is on when power is applied to the module, and one input status indicator for each input (12 in all).

$\mathbf{A} = \text{Power/status indicator} - \text{indicates power applied to module}$  and status of module.

**B** = Insertable label for writing individual I/O assignments.

**C** = Status Indicators –

A = Status of input A

$\mathbf{B} = \mathbf{S}$ tatus of input B

$\mathbf{Z}$  = Status of input  $\mathbf{Z}$

G = Status of input G

+ = Positive count detected

-= Negative count detected

| Indicator | Indication | Explanation                                                        |  |  |

|-----------|------------|--------------------------------------------------------------------|--|--|

| Α         | Yellow     | Input A active                                                     |  |  |

|           | Off        | Input A not active                                                 |  |  |

| В         | Yellow     | Input B active                                                     |  |  |

|           | Off        | Input B not active                                                 |  |  |

| Z         | Yellow     | Input Z active                                                     |  |  |

|           | Off        | Input Z not active                                                 |  |  |

| G         | Yellow     | Input G active                                                     |  |  |

|           | Off        | Input G not active                                                 |  |  |

| +         | Yellow     | On when a positive pulse is detected; turns off on negative pulse. |  |  |

| -         | Yellow     | On when a negative pulse is detected; turns off on positive pulse. |  |  |

| ОК        | Red        | Red during initialization after power turned on                    |  |  |

|           | Green      | Green when initialization is completed                             |  |  |

## **Chapter Summary**

In this chapter, we told you how to install your incrementa encoder module in an existing programmable controller system and how to wire to the terminal base units.

## Programming Your Incremental Encoder Module

## What This Chapter Contains

To initiate communication between the incremental encoder module and your PLC processor, you must enter block transfer instructions into your ladder logic program. Use this chapter to enter the necessary block transfer instructions into your ladder logic program.

| To edit your ladder logic you     | See page |

|-----------------------------------|----------|

| Enter Block Transfer Instructions | 3–1      |

| PLC-2 Family Processors           | 3-2      |

| PLC-5 Family Processors           | 3-2      |

| SLC-5 Processors                  | 3-3      |

## **Enter Block Transfer Instructions**

The incremental encoder module communicates with the PLC processor through bidirectional block transfers. This is the sequential operation of both read and write block transfer instructions.

Before you configure the module, you need to enter block transfer instructions into your ladder logic. The following example programs illustrate the minimum programming required for communication to take place between the module and a PLC processor. These programs can be modified to suit your application requirements.

A configuration block transfer write (BTW) is initiated when the module is first powered up, and subsequently only when the programmer wants to enable or disable features of the module. The configuration BTW sets the bits which enable the programmable features of the module, such as scalars and alarm values, etc. Block transfer reads are performed to retrieve information from the module.

Block transfer read (BTR) programming moves status and data from the module to the processor's data table. The processor user program initiates the request to transfer data from the module to the processor. The transferred words contain module status, channel status and input data from the module.

Your program should monitor status bits, block transfer read and block transfer write activity.

#### **PLC-2 Family Processor**

The 1794 incremental encoder module is not recommended for use with PLC-2 family programmable controllers due to the number of digits needed for high resolution.

Important:

The incremental encoder module functions with reduced performance in PLC-2 systems. Because the module does not support BCD and the PLC-2 processor is limited to values of 4095 (12 bit binary), many values returned in the BTR file may not provide meaningful data to the PLC-2 processor.

#### **PLC-5 Family Processor**

Block transfer instructions with the PLC-5 processor use a control file and a data file. The block transfer control file contains the data table section for module location, the address of the block transfer data file and other related data. The block transfer data file stores data that you want transferred to the module (when programming a BTW) or from the module (when programming a BTR).

The programming terminal prompts you to create a control file when a block transfer instruction is being programmed. A different block transfer control file is used for the read and write instructions for your module.

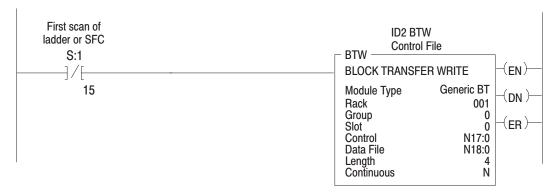

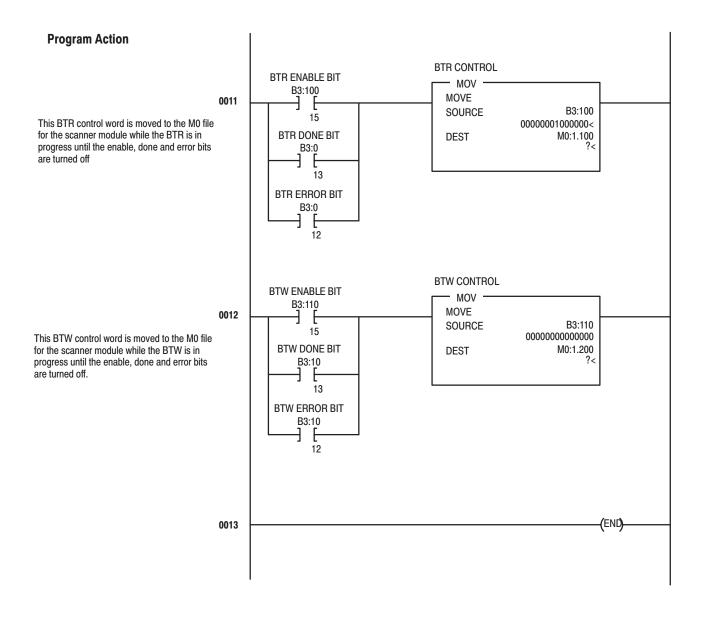

PLC-5 Processor Program Example Rung 2:0

The ID2 module is located in rack 1, I/O group 0, slot 0. The integer control file starts at N17:0. The data sent by the PLC-5 processor to the ID2 module starts at N18:0 and is 4 words long. At power up in RUN mode, or when the processor is first switched from PROG to RUN, the user program enables a block transfer write to configure the module..

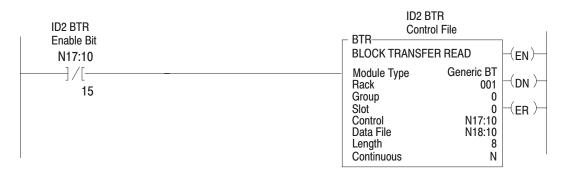

Rung 2:1

The ID2 module is located in rack 1, group 2, slot 0. The integer control file starts at N17:10,. The data obtained by the PLC-5 processor from the ID2 module is placed in memory starting at N18:10 and is 8 words long. IThe program continuously performs read block transfers to read data from the module.

#### **SLC-5 Programming**

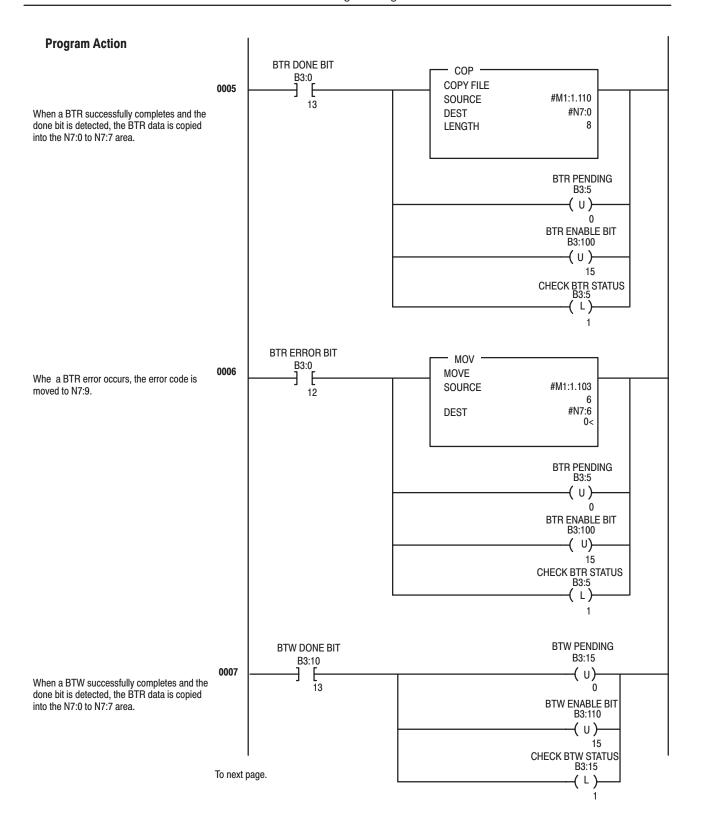

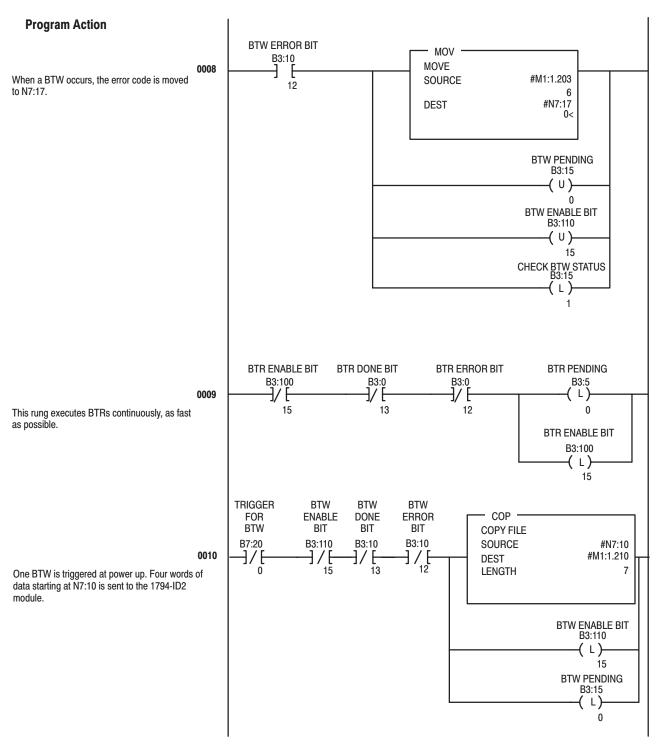

The SLC-5 programs (using the 1747-SN scanner) follow the same logic as the PLC-5 family programs in the previous example. Differences occur in the implementation of block transfers due to the use of "M" files in the SLC system.

Configuration data for the FLEX I/O incremental encoder module and the 1747-SN scanner must be in place before executing the following programs. Chapter 4 contains information on module configuration.

For more information on using the 1747-SN scanner module and block transfer programming, refer to publication 1747-6.6, "Remote I/O Scanner User Manual."

BTR\_CONTROL **Program Action** PowerUp Bit - COP -**COPY FILE** [-15 0000 SOURCE #B3:100 This rung configures the block transfer operation DEST #M0:1.100 type, length, and RIO address at power-up. Bit LENGTH 3 B3:100/7 must be set to 1 to indicate a BTR and bit B3:110/7 must be 0 to indicate a BTW. BTW\_CONTROL COP -**COPY FILE** #B3:110 SOURCE #M0:1.200 DEST LENGTH 3 BTR PENDING COP -**COPY FILE** 0001 #M1:1.100 SOURCE BTR status is copied to the B3:0 area when a BTR #B3:0 **DEST** is in progress. LENGTH CHECK BTR STATUS B3:5 **CHECK BTR STATUS** BTR DONE BIT B3:5 B3:0 0002 ( U) Unlatch the bit that continues to check the BTR status. BTR ERROR BIT B3:0 12 BTW PENDING COP -**COPY FILE** 0003 #M1:1.200 SOURCE BTW status is copied to the B3:100 area when a #B3:10 **DEST** BTW is in progress. LENGTH 4 CHECK BTW STATUS B3:15 **CHECK BTW STATUS** BTW DONE BIT B3:15 B3:10 Unlatch the bit that continues to check the BTW status. BTW ERROR BIT B3:10 To next page. 12

Figure 3.1SLC Programming for the 1794-OF4I Isolated Analog Output Module

To next page.

#### **Chapter Summary**

In this chapter, you learned how to program your ID2 incremental encoder module using block transfer instructions and ladder logic. Now, you can configure your module.

# Writing Configuration to and Reading Status from Your Module with a Remote I/O Adapter

## What This Chapter Contains

In this chapter, we tell you about:

| For information on                                        | See page |

|-----------------------------------------------------------|----------|

| Configuring Your Module                                   | 4–1      |

| Reading Data from Your Module                             | 4–2      |

| Mapping Data for the Module                               | 4–2      |

| Incremental Encoder Module (1794-ID2) Image Table Mapping | 4-2      |

| Block Transfer Read Word Assignments                      | 4–3      |

| Bit/Word Definitions for Block Transfer Read Words        | 4-3      |

| Block Transfer Write Word Assignments                     | 4–5      |

| Bit/Word Definitions for the Block Transfer Write Words   | 4-5      |

## Configuring Your Incremental Encoder Module

The incremental encoder module is configured using a group of data table words that are transferred to the module using a block transfer write instruction.

Some of the software configurable features available are:

- number of inputs

- encoder multiplier

- gate function

- latch function

- rollover

Configure your module for its intended operation by means of your programming terminal and write block transfers.

**Note:** Programmable controllers that use 6200 software (release 4.2 or higher) programming tools can take advantage of the IOCONFIG Addendum utility to configure this module. IOCONFIG Addendum uses menu—based screens for configuration without having to set individual bits in particular locations. Refer to your 6200 software literature for details.

#### **Important:**

It is strongly recommended that you use IOCONFIG Addendum to configure this module. The IOCONFIG Addendum utility greatly simplifies configuration. If the IOCONFIG Addendum is not available, you must enter data directly into the data table. Use this chapter as a reference when performing this task.

During normal operation, the processor transfers from 1 to 4 words to the module when you program a BTW instruction to the module's address.

## Reading Data From Your Module

Read programming moves status and data from the frequency input module to the processor's data table in one I/O scan. The processor's user program initiates the request to transfer data from the incremental encoder module to the processor.

## Mapping Data for the Module

The following read and write words and bit/word descriptions describe the information written to and read from the incremental encoder module. The module uses up to 8 words of input data and up to 5 words of output data. Each word is composed of 16 bits.

## Incremental Encoder Module (1794-ID2) Image Table Mapping Module Image

| R | PR1                                         | PR0 | S1 | S0 | C1   | CO    | G1     | Z1    | B1  | <b>A</b> 1 | G0    | <b>Z</b> 0 | В0 | A0 |

|---|---------------------------------------------|-----|----|----|------|-------|--------|-------|-----|------------|-------|------------|----|----|

|   | Store 0 - Stored Counter Value on channel 0 |     |    |    |      |       |        |       |     |            |       |            |    |    |

|   | Store 1 – Stored Counter Value on channel 1 |     |    |    |      |       |        |       |     |            |       |            |    |    |

|   | Channel 0 – current counter value           |     |    |    |      |       |        |       |     |            |       |            |    |    |

|   |                                             |     |    |    | Cha  | nnel  | 1 – cı | urren | cou | nter v     | alue  |            |    |    |

|   |                                             |     |    |    | Char | nel 0 | - Co   | unter | wor | d read     | lback | (          |    |    |

|   | Channel 1 – Counter word readback           |     |    |    |      |       |        |       |     |            |       |            |    |    |

|   | Code for identification of software version |     |    |    |      |       |        |       |     |            |       |            |    |    |

| Channel 0 Control Word – Sets the function of counter 0    |

|------------------------------------------------------------|

| Channel 1 Control Word – Sets the function of counter 1    |

| Channel 0 Preset – value to load or compare with counter 0 |

| Preset 1 – value to load or compare with counter 1         |

| Control Word 2 – Sets filter function for both counters    |

#### **Block Transfer Read Word Assignments for the Incremental Encoder Module (1794-ID2)**

| (Octal Bit⇒)           | 17   | 16                                            | 15  | 14  | 13 | 12     | 11        | 10       | 07        | 06       | 05       | 04 | 03 | 02 | 01 | 00 |

|------------------------|------|-----------------------------------------------|-----|-----|----|--------|-----------|----------|-----------|----------|----------|----|----|----|----|----|

| Dec. Bit $\Rightarrow$ | 15   | 14                                            | 13  | 12  | 11 | 10     | 09        | 08       | 07        | 06       | 05       | 04 | 03 | 02 | 01 | 00 |

| Word↓                  |      |                                               |     |     |    |        |           | Rea      | d         |          |          |    |    |    |    |    |

| 0                      | CTD1 | CTD0                                          | PR1 | PR0 | S1 | S0     | C1        | C0       | G1        | Z1       | B1       | A1 | G0 | Z0 | B0 | A0 |

| 1                      |      | Channel 0 - Stored counter value on channel 0 |     |     |    |        |           |          |           |          |          |    |    |    |    |    |

| 2                      |      |                                               |     |     | C  | hannel | 1 – Stor  | ed coun  | ter valu  | ie on cl | nannel 1 |    |    |    |    |    |

| 3                      |      |                                               |     |     | С  | hannel | 0 – curre | ent coun | iter valu | ie on c  | hannel 0 |    |    |    |    |    |

| 4                      |      |                                               |     |     | С  | hannel | 1 – curre | ent coun | iter valu | ie on c  | hannel 1 |    |    |    |    |    |

| 5                      |      | Channel 0 – Counter word readback             |     |     |    |        |           |          |           |          |          |    |    |    |    |    |

| 6                      |      | Channel 1 – Counter word readback             |     |     |    |        |           |          |           |          |          |    |    |    |    |    |

| 7                      |      |                                               |     |     |    | Revi   | sion rea  | d – soft | vare ve   | ersion c | ode      |    |    |    |    |    |

Where: A0 = Status of input A, channel 0 - bit = 1 when input is on

B0 = Status of input B, channel 0 - bit = 1 when input is on

Z0 = Status of input Z, channel 0 - bit = 1 when input is on

G0 = Status of input G, channel 0 - bit = 1 when input is on

G1 = Status of input G, channel 1 - bit = 1 when input is on

A1 = Status of input A, channel 1 - bit = 1 when input is on

B1 = Status of input B, channel 1 - bit = 1 when input is on

Z1 = Status of input Z, channel 1 - bit = 1 when input is on C0 = Cal 0 - when bit is set, counter 0 has been calibrated (reset by CalReset)

C1 = Cal 1 - when bit is set, counter 1 has been calibrated (reset by CalReset)

S0 = Stored 0 – when bit is set, counter 0 value has been saved in Store 0 (reset by StoreReset)

S1 = Stored 1 - when bit is set, counter 1 value has been saved in Store 1 (reset by StoreReset)

Once a Store occurs, L0 and L1 are on until cleared by StoreReset (counter word bit 14)

PR0 = Preset 0 reached - when bit is set, counter 0 has reached value of preset

(reset by PresetReset) PR1 = Preset 1 reached - when bit is set, counter 1 has reached value of preset

(reset by PresetReset)

#### Bit/Word Definitions for Block Transfer Read Words for the **Incremental Encoder Module**

| Read<br>Word | Bit    | Definition                                                                              |

|--------------|--------|-----------------------------------------------------------------------------------------|

|              | Bit 00 | Status for input A (pulse transmitter 0) - This bit, when set, indicates a signal at A. |

|              | Bit 01 | Status for input B (pulse transmitter 0) - This bit, when set, indicates a signal at B. |

| Word 0       | Bit 02 | Status for input Z (pulse transmitter 0) - This bit, when set, indicates a signal at Z. |

| Word 0       | Bit 03 | Status for input G (pulse transmitter 0) -This bit, when set, indicates a signal at G.  |

|              | Bit 04 | Status for input A (pulse transmitter 1) - This bit, when set, indicates a signal at A. |

|              | Bit 05 | Status for input B (pulse transmitter 1) - This bit, when set, indicates a signal at B. |

| Read<br>Word     | Bit                   | Definition                                                                                                                                                                                                                                                         |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|